出展者詳細情報国立大学法人熊本大学(末吉研究室)(プログラマブル デバイスプラザ)

国立大学法人熊本大学(末吉研究室)(プログラマブル デバイスプラザ)

- 住所

- 〒860-8555 熊本県熊本市中央区黒髪2-39-1

- ステージ

- NEXT イノベーションエリア

- ホール

- ホール3

- 小間番号

- 3N17-4

会社紹介

熊本大学末吉研究グループでは以下の4つのテーマを取り扱っている.

・次世代コンピュータシステムの基盤研究

・ディペンダブルシステムに関する研究

・3次元リコンフィギャラブルロジックとその応用

・やわらかいハードウェアとVLSI設計技術

出展製品

出展製品情報 1

IC(集積回路)

日の丸FPGA(その1) 3D-FPGA, FeRAM搭載FPGA

FPGAは製造後に回路をプログラマブル可能という特徴をもつ反面,組込みシステムとして使用する際は消費電力が問題となる.

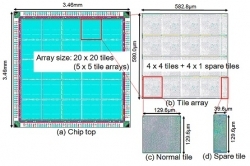

本ブースでは3次元積層技術とFPGAを組合わせた3次元FPGAの紹介を行う.

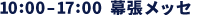

また,低消費電力化の観点より我々が開発したFerroelectric random access memory (FeRAM) ベースFPGAの展示を行う.本FPGAでは構成メモリに不揮発FlipFlop を使用することで,チップの電源の投入/遮断を検知し,FFとFeRAM間でデータを自動で退避/復帰を可能としている.

主な研究成果:

M.Amagasaki, Q.Zhao, M.Iida, M.Kuga and T.Sueyoshi,

"A 3D FPGA Architecture to Realize Simple Die Stacking",

IPSJ Transactions on System LSI Design Methodology, Vol.8,pp.116-122, Aug. 2015

M.Iida, M.Koga, K.Inoue, M.Amagasaki, Y.Ichida, M.Saji, J.Iida and T.Sueyoshi

"A Genuine Power-Gatable Reconfigurable Logic Chip with FeRAM Cells",

IEICE Transactions on Electronics, Vol.E94-C, No.4, pp.548-556 ,Apr. 2011

出展製品情報 2

IC(集積回路)

日の丸FPGA(その2) FT-FPGA

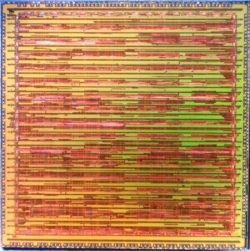

信頼性が要求されるシステムではTMR(Tripple Module Redundancy)のように対象モジュールの多重化が使われることが多い.特に,SoC に搭載されるFPGA-IPコアを対象とした場合,面積制約が非常に大きいため単純な冗長化は困難である.我々の提案するFT-FPGA は決まったタイル数毎にスペアタイルを備え,故障が起きた際に回路を退避させることで信頼性を上げている.また,FT-FPGA はソフトIP コアとして提供されるため,通常のASIC(Application Specific Integrate Circuit)設計ツールを用いてSoC に搭載可能である.

主な研究成果:

M.Amagasaki, Kazuki Inoue, Q.Zhao, M.Iida, M.Kuga and T.Sueyoshi,

"DEFECT-ROBUST FPGA ARCHITECTURES FOR INTELLECTUAL PROPERTY CORES IN SYSTEM LSI,"

Proc. of 23th International Conference on Field Programmable Logic and Applications (FPL2013), porto, porutugal, Sep. 2013.

出展製品情報 3

システム LSI(SoC)

自己修復ディペンダブルシステム

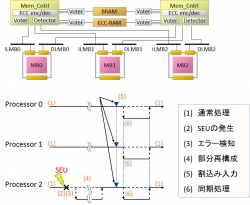

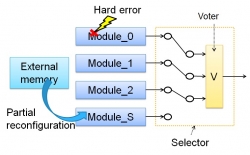

組込みシステム開発用のプラットフォームとしてFPGAを採用することが一般的になってきた現在,FPGAの信頼性が非常に重要視されている.我々はSRAM型FPGAを対象として,放射線起因のソフトエラー,および偶発故障によるハードエラーを対象としたディペンダブルシステムの研究を行っている.ソフトエラーを対象とした提案ソフトコアプロセッサは,エラー検出後割込み動作により内部コンテキストの同期を行い,通常動作に自動的に復旧する. 一方,ハードエラーに対しては部分再構成を用いてスペアモジュールに回路情報を移動することで故障回避を行う.

主な研究成果:

Y.Ichinomiya, S.Usagawa, M.Amagasaki, M.Iida, M.Kuga and T.Sueyoshi,

"Designing flexible reconfigurable regions to relocate partial bitstreams,"

Proc. the 20th Annual International IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM2012), pp.241, Toronto, Canada, May 2012

一ノ宮佳裕,石田智之,田上士郎,尼崎太樹,久我守弘,末吉敏則

"SRAM型FPGAの部分再構成によるソフトコアプロセッサの高信頼化,"

信学論,vol.J92-D,no.12,pp.2105-2113,Dec. 2009.

お問い合わせ先

- 住所

- 〒860-8555 熊本市中央区黒髪2-39-1

- 担当部署名

- 熊本大学大学院自然科学研究科

- 担当者名

- 末吉敏則

- TEL

- 096-342-3629

- FAX

- 096-342-3630

- メールアドレス1

- sueyoshi@cs.kumamoto-u.ac.jp

プレスの方お問い合わせ先

- 住所

- 〒860-8555 熊本市中央区黒髪2-39-1

- 担当部署名

- 熊本大学大学院自然科学研究科

- 担当者名

- 末吉敏則

- TEL

- 096-342-3629

- FAX

- 096-342-3630

- メールアドレス1

- sueyoshi@cs.kumamoto-u.ac.jp